Summary − So this instruction NOP requires 1-Byte, 1-Machine Cycle (Opcode Fetch) and 4 T-States for execution as shown in the timing diagram. The timing diagram against this instruction NOP execution is as follows −

Otherwise “Insert” and “Delete” keys are available on our microprocessor kit, which might help us for new code insertion and pre-existing code deletion. Thus, it is a good programming practice to have a few NOP instructions in the program at regular intervals od code, especially during program development. In future when extra code is to be inserted then we can replace NOP instructions and can do needful accordingly. NOP instruction is very useful when we require to keep some memory space void with in our program for future instruction insertions accordingly. So introduction of this NOP instruction can produce synchronization of the speed between these two. It is very useful for generating small-time delays of the order of a few microseconds.Ĩ085 Microprocessor works faster compared to the speed of its other peripheral devices. NOP instruction can be used to create small-time delay in the execution of the code. In spite of the fact that it does nothing, still it has got many different applications. Only it occupied 1-Byte of memory space and spends 4-Machine Cycles. This instruction does nothing during execution. NOP is a mnemonic that stands for “No Operation”. Summary − So this instruction INR M requires 1-Byte, 3-Machine Cycles (Opcode Fetch, Memory Read, Memory Write) and 10 T-States for execution as shown in the timing diagram.In 8085 Instruction set, NOP is an instruction which is falling under Machine Control Instruction category. The instructions which have more than one byte word size will use the machine cycle after the opcode fetch machine cycle.

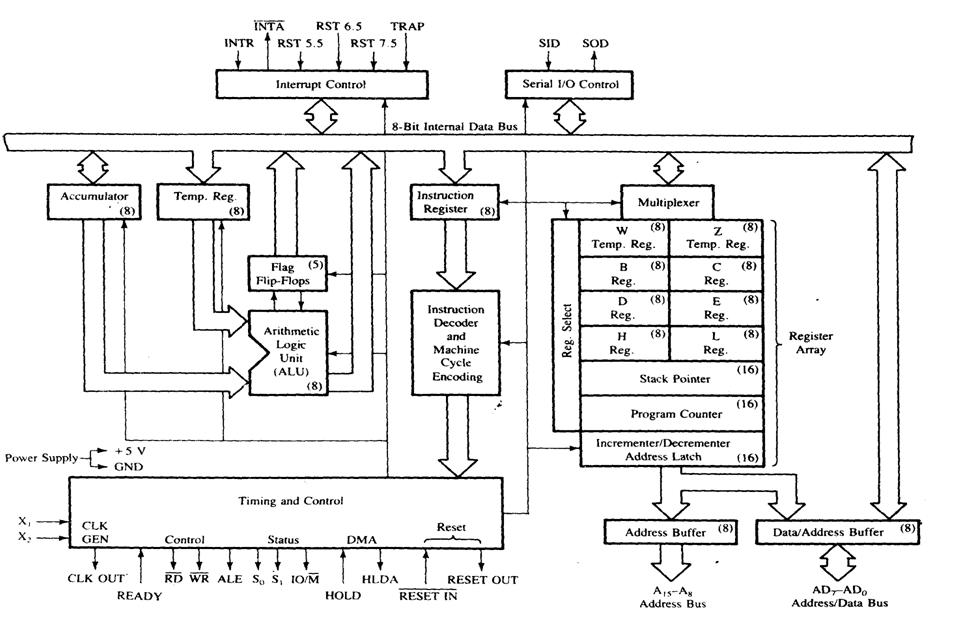

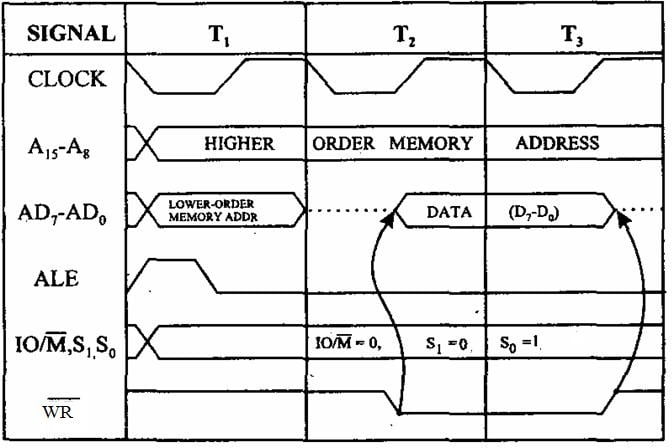

The processor takes 3T states to execute this cycle. Here is the timing diagram of the execution of the instruction INR M The memory read machine cycle is executed by the processor to read a data byte from memory. 4050H memory locations content will be increased by 1 as HL register pair is having 16-bit address 4050H The tracing table of this instruction is as follows Such a graphical representation is called timing diagram. The descriptions of various pins are as follows: Address Bus and Data Bus. So after execution of the instruction INR M, the current content of location 4050H will become 06H. Fig: Pin diagram of Intel 8085 microprocessor. Let us consider that HL register pair is holding the 16-bit value 4050H as 16-bit address. There are some output signals in 8085 that tell us about the processes going on inside the microprocessor. Let us consider INR M as a sample instruction of this category. As R can have any of the eight values as mentioned, so there are eight opcodes possible for this type of instruction. In different assembly language core, this instruction is used for looping or as a count.

The 8085 µP instruction cycle consists of one to five m/c cycles or one to five operations. The different types of cycles used in the timing diagram representation are as follows: Instruction Cycle: Instruction cycle is defined as the time required completing the execution of an instruction. All flags, except Cy flag, are affected depending on the result thus produced. The execution time is represented in T-states. The result of increment will be stored in R updating its previous content. So the previous value in R will get increased by amount 1 only. This instruction is used to add 1 with the contents of R. In 8085 Instruction set, INR is a mnemonic that stands for ‘INcRement’ and ‘R’ stands for any of the following registers or memory location M pointed by HL pair.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed